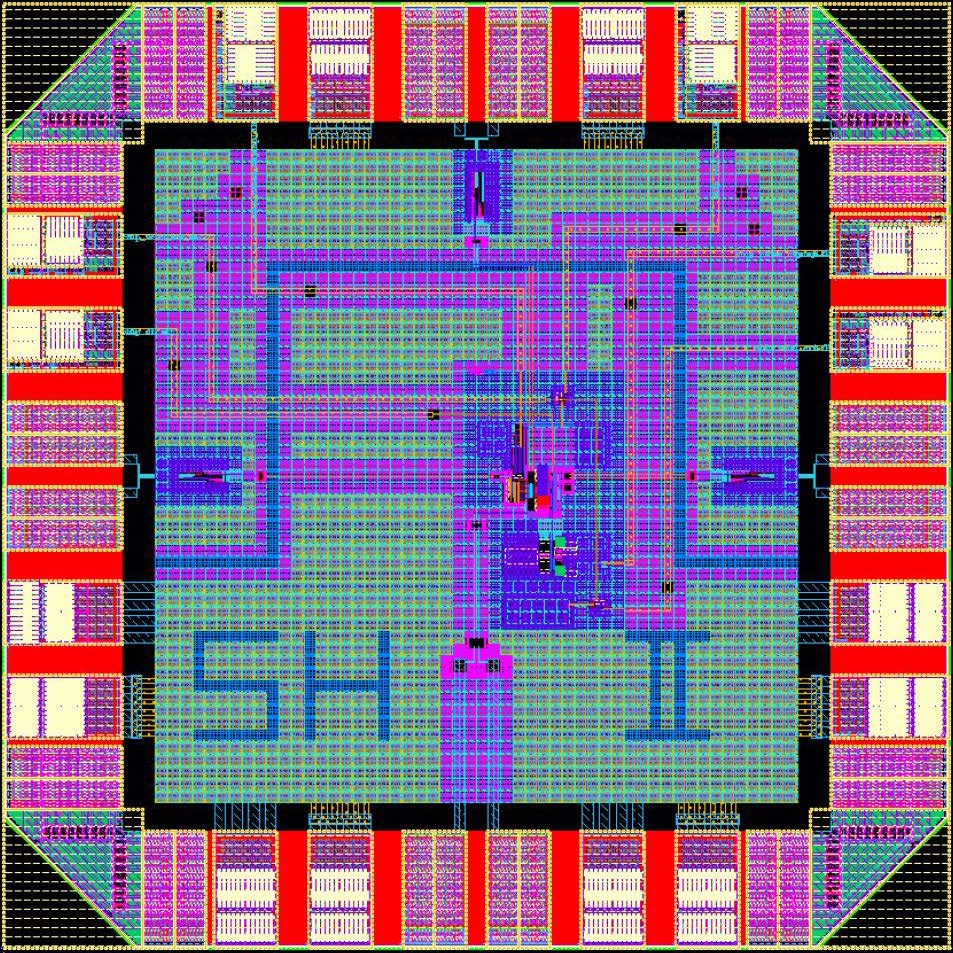

Chip Gallery

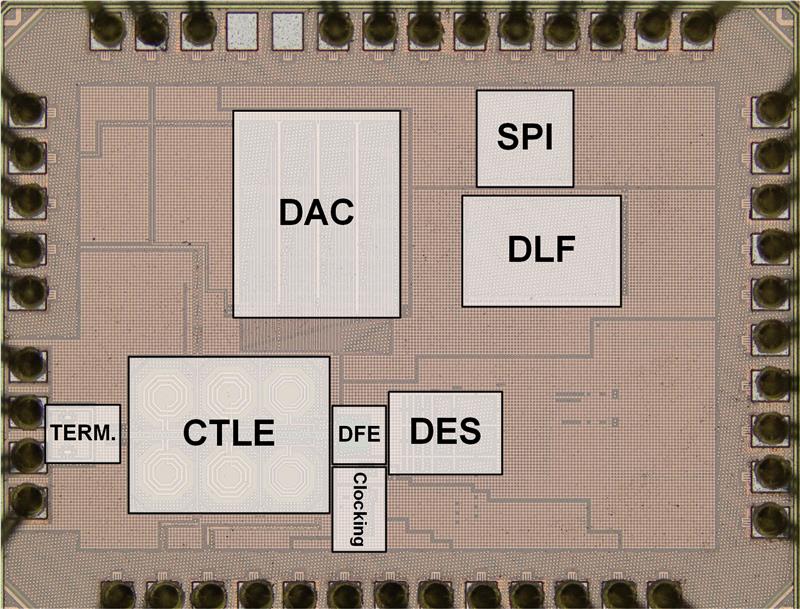

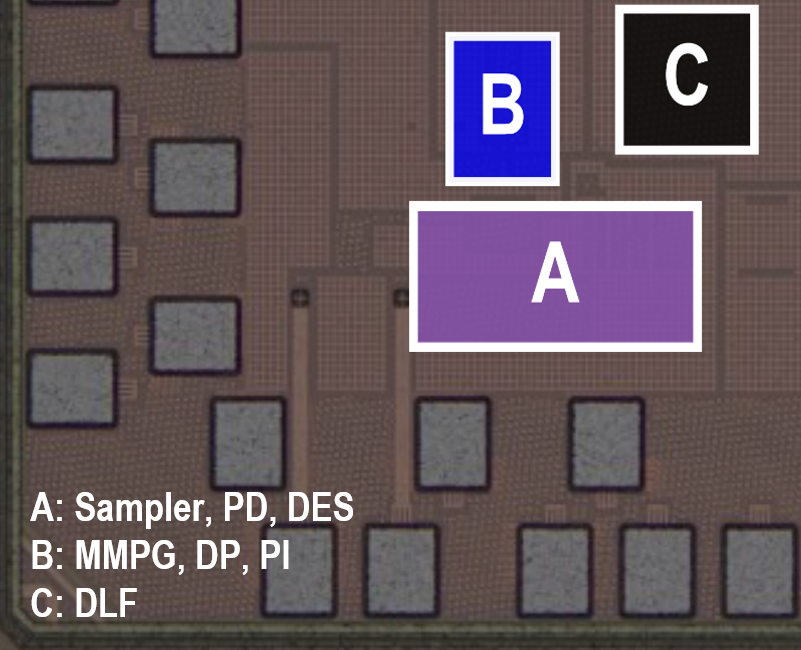

High-Speed PAM-4 Receiver

- Date: Sep. (28-nm T)'25

- Designer: Seung-Hwan Gong

- Description: N/A

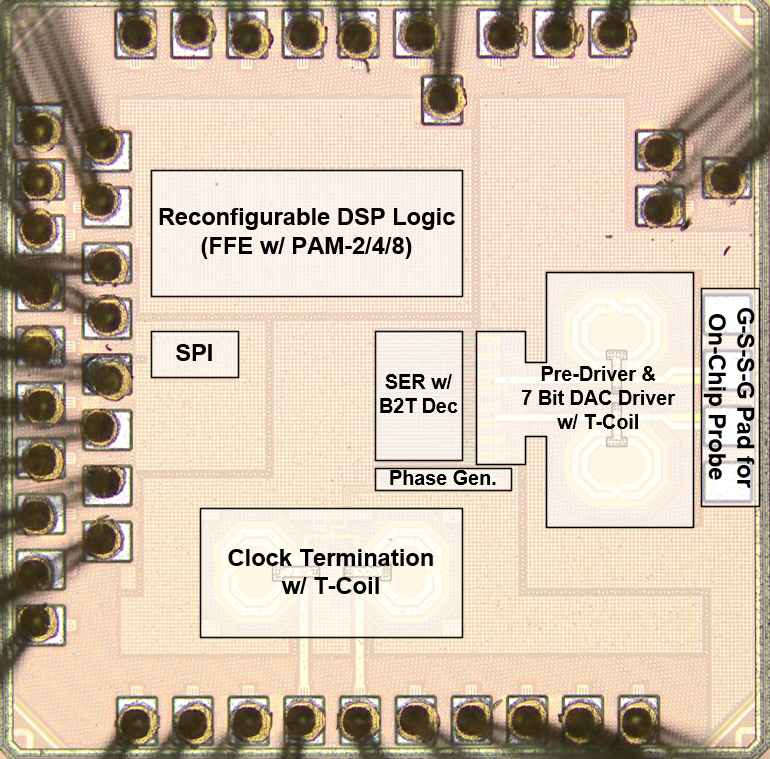

High-Speed Transmitter

- Date: Sep. (28-nm T)'25

- Designer: Dong-Ho Kim and Seung-Mo Jin

- Description: N/A

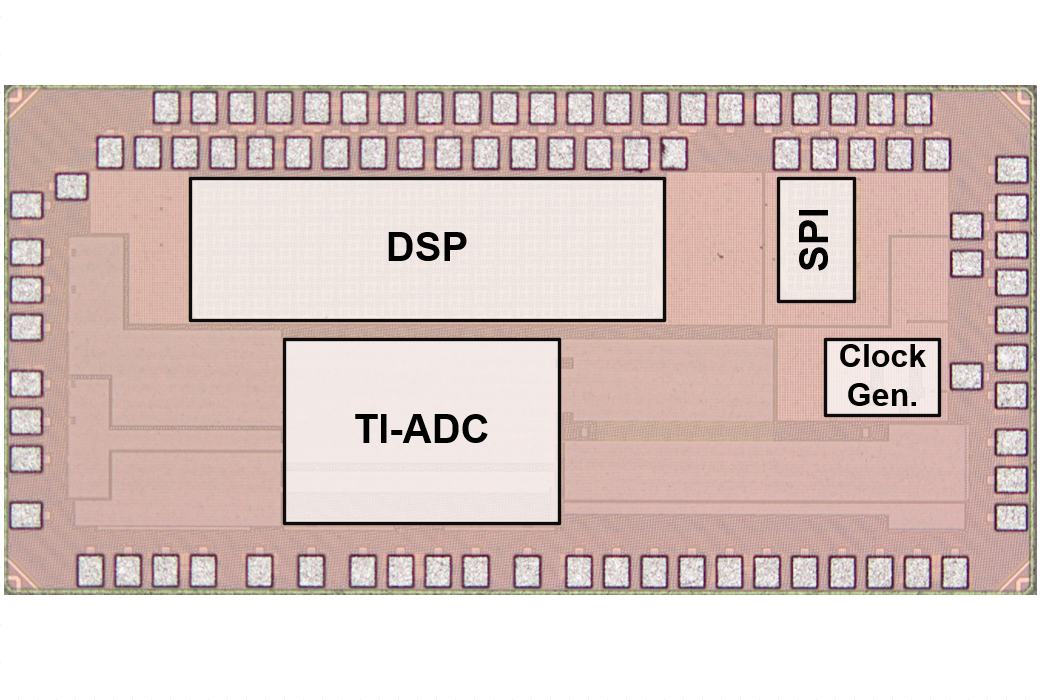

DSP-based High-Speed Receiver

- Date: Jul. (28-nm T)'25

- Designer: Jae-Geon Lee

- Description: N/A

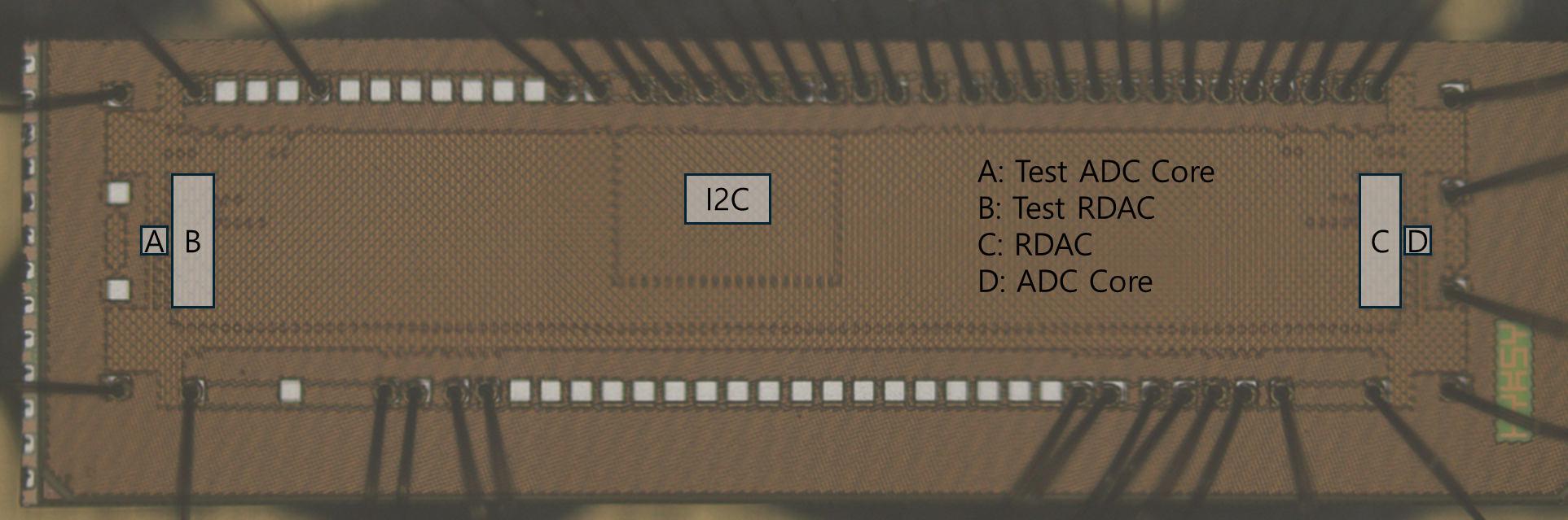

2GS/s SAR ADC for Cryogenic

- Date: Jul. (28-nm SS)'25

- Designer: Dong-Eon Jin

- Description: N/A

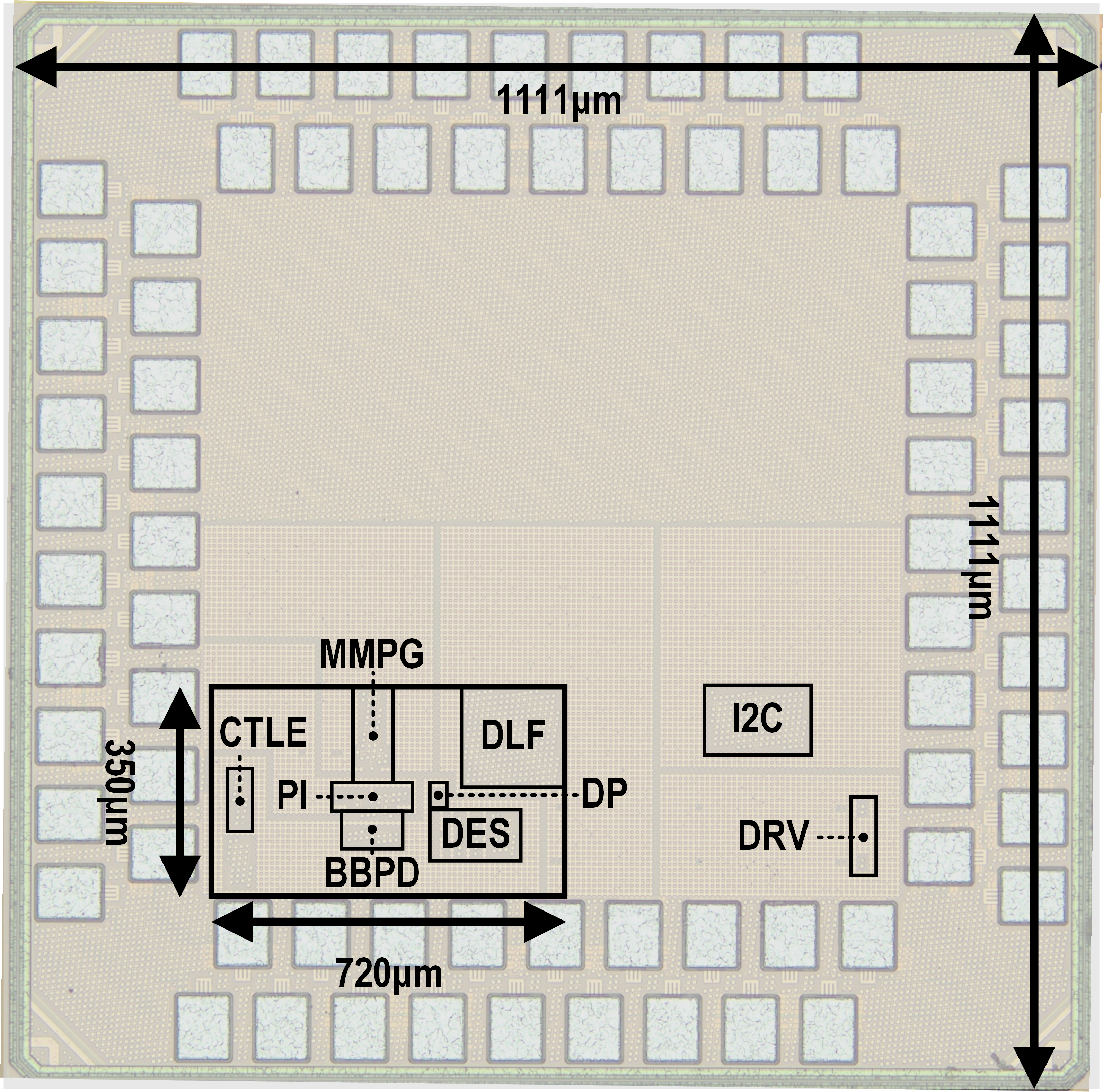

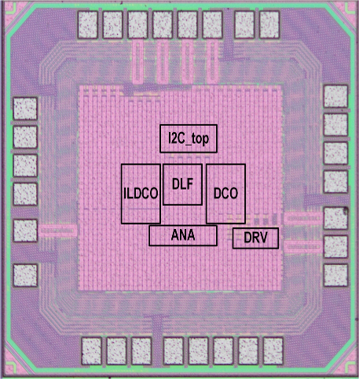

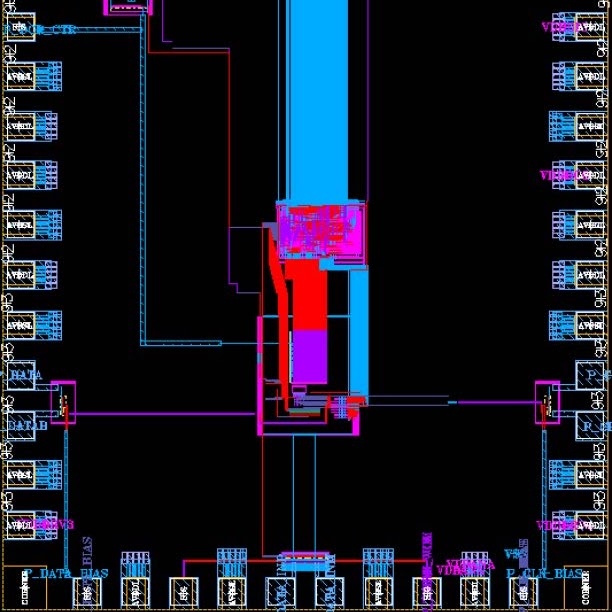

PI-based CDR

- Date: Feb. (28-nm T)'25

- Designer: Dong-Hoe Heo

- Description: Digital Analog revision

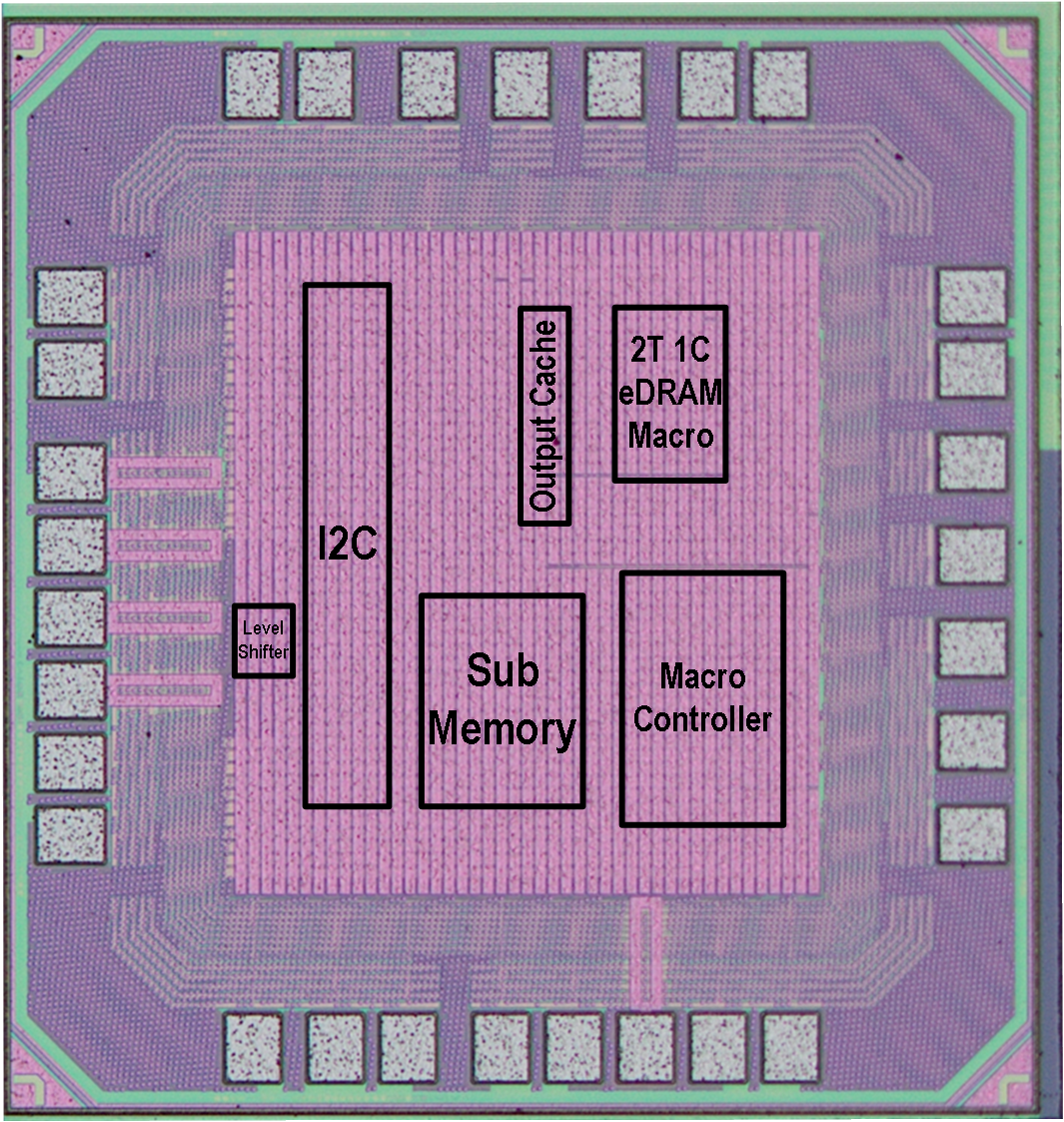

2T eDRAM PIM

- Date: Nov. (65-nm T)'24

- Designer: Dong-Hyun Lee

- Description: Digital Analog revision

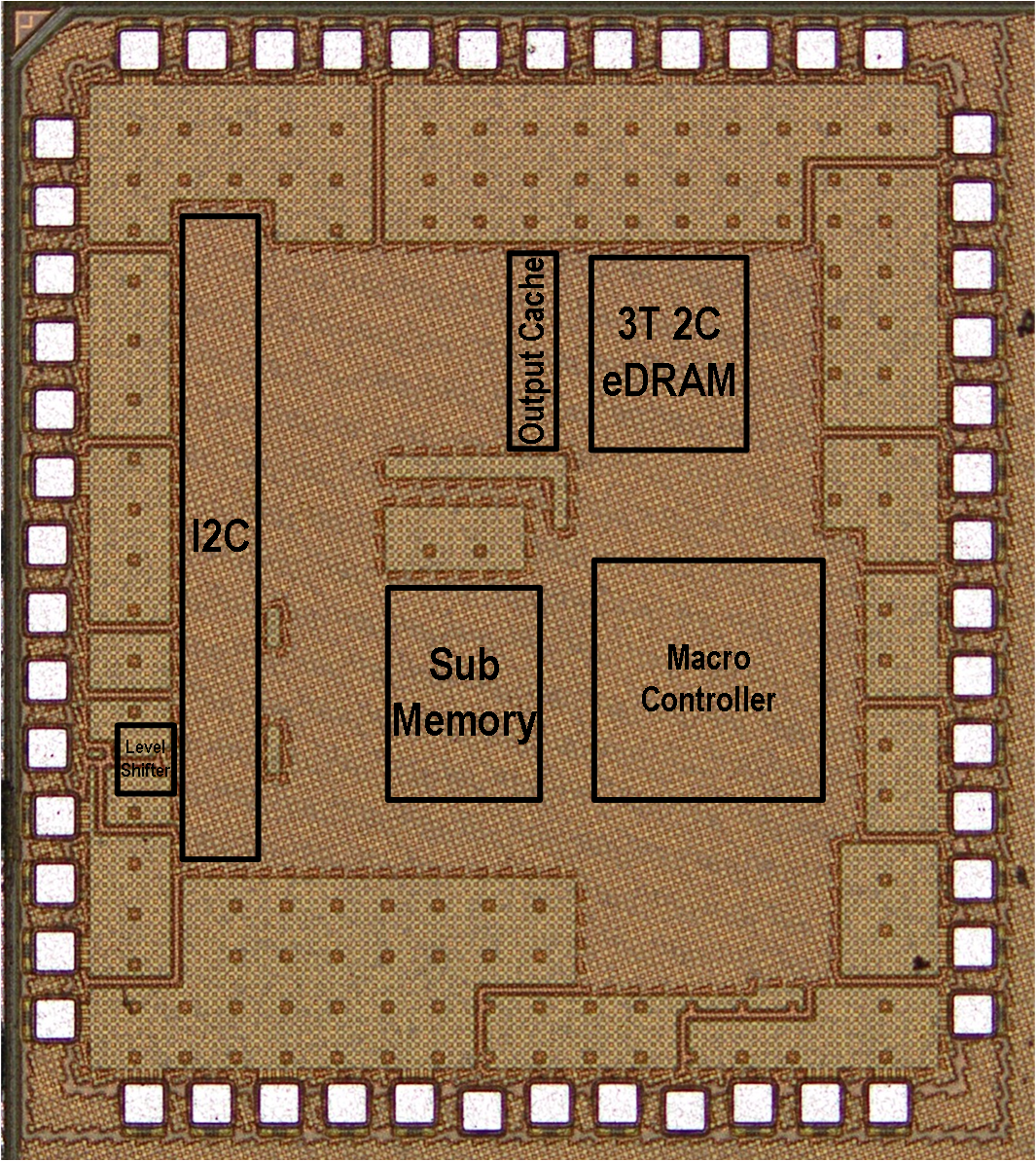

3T eDRAM PIM

- Date: Nov. (65-nm T)'24

- Designer: Dong-Hyun Lee

- Description: Digital Analog revision

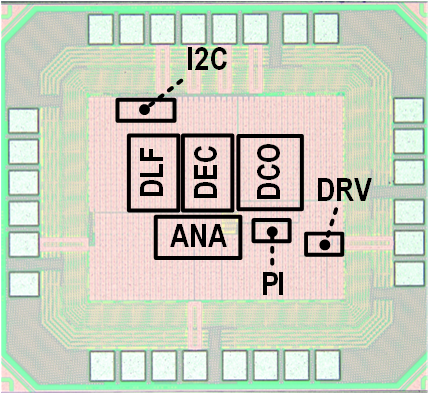

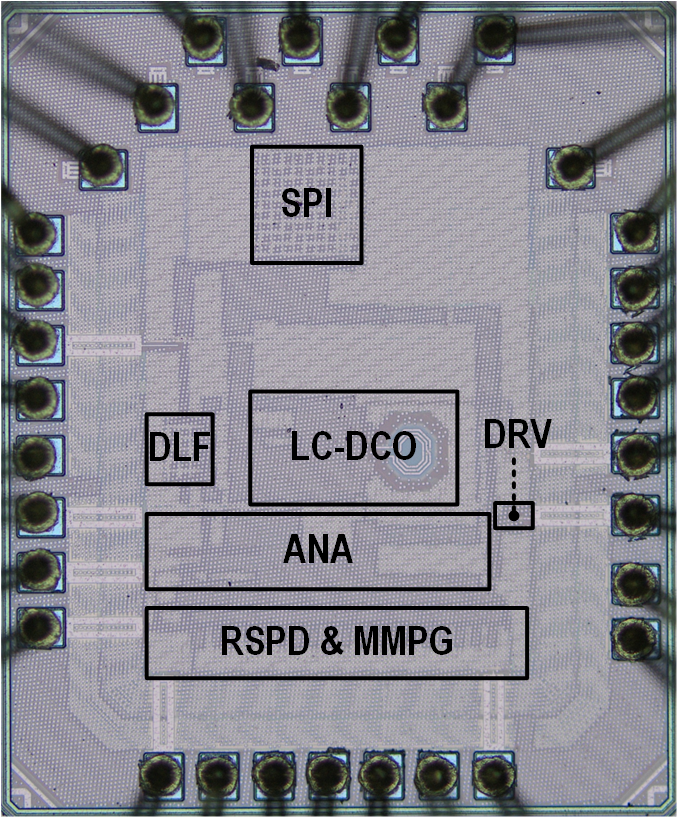

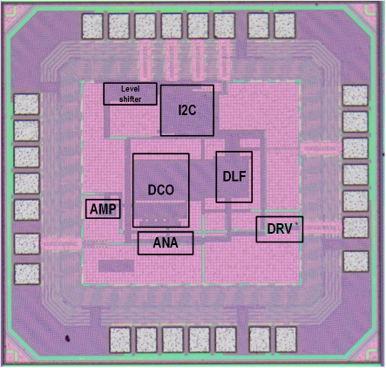

PI ADPLL

- Date: Oct. (65-nm T)'24

- Designer: Kyu-Ran Park

- Description: N/A

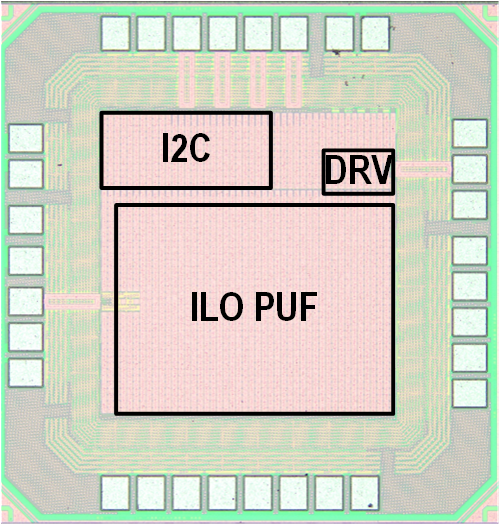

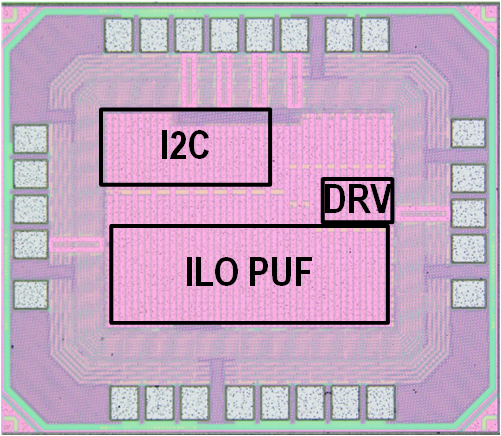

ILO-based PUF

- Date: Oct. (65-nm T)'24

- Designer: Kang-Min Kim

- Description: Analog revision

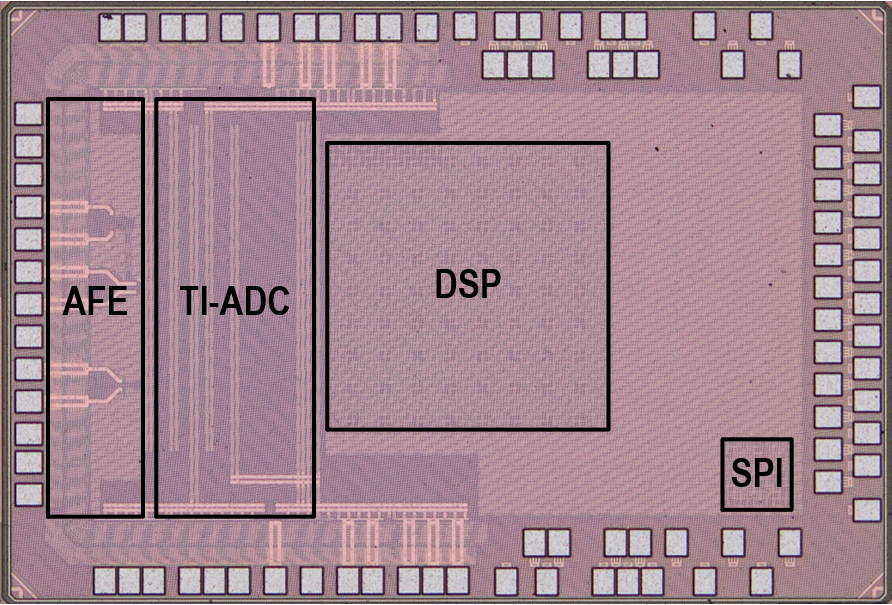

ADC-based DSP RX

- Date: Oct. (40-nm T)'24

- Designer: Sang-Hyeon Ok

- Description: failed

Oversampling PLL

- Date: Oct. (40-nm T)'24

- Designer: Ji-Ho Kim

- Description: N/A

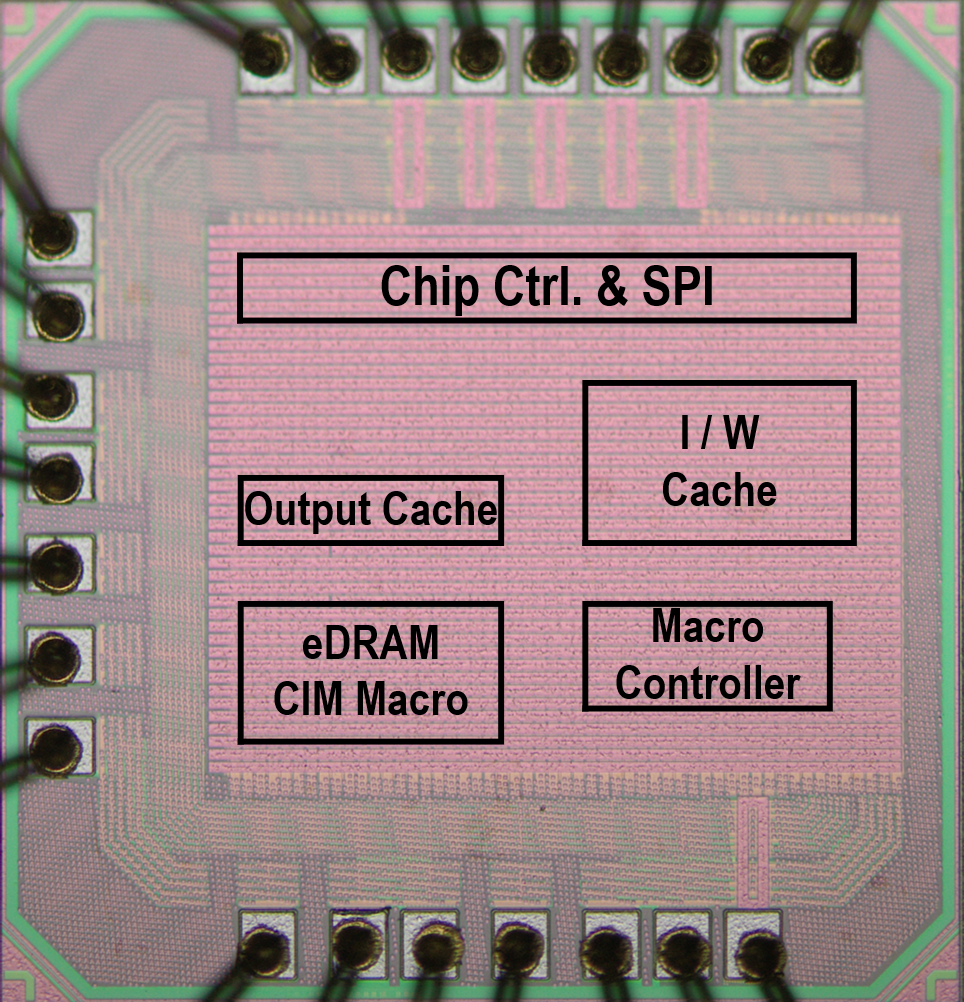

3T eDRAM PIM

- Date: Jul (65-nm T)'24

- Designer: Woo-Suk Jeong

- Description: failed

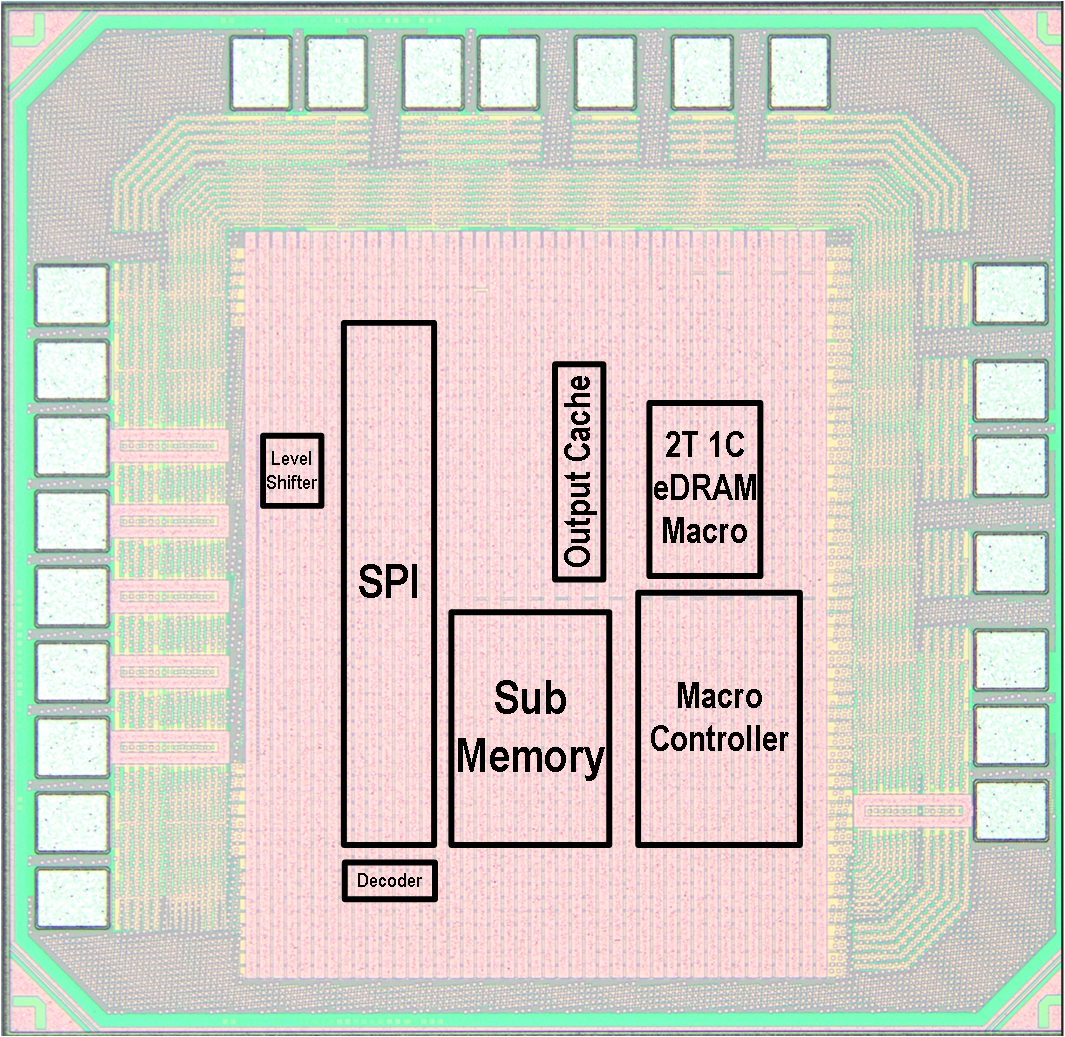

2T eDRAM PIM

- Date: May (65-nm T)'24

- Designer: Dong-Hyun Lee

- Description: failed

ILO-based PUF

- Date: May (65-nm T)'24

- Designer: Kang-Min Kim

- Description: failed

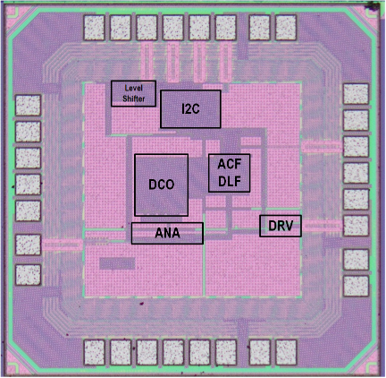

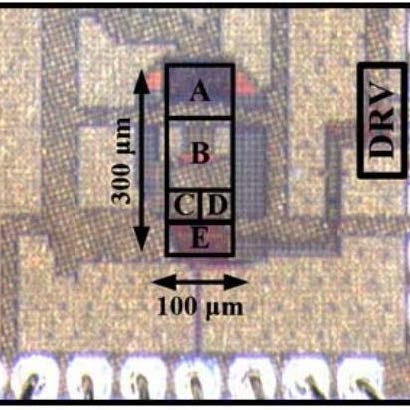

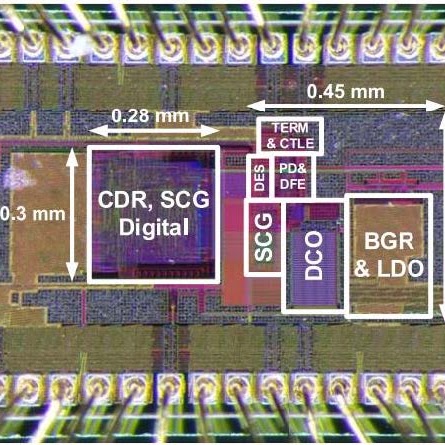

PI-based CDR

- Date: June (28-nm T)'24

- Designer: Dong-Hoe Heo

- Description: N/A

Supply Noise Insensitive ADPLL

- Date: Dec (65-nm T)'23

- Designer: N/A

- Description: N/A

ADPLL ILO Calibration

- Date: Dec (65-nm T)'23

- Designer: N/A

- Description: failed

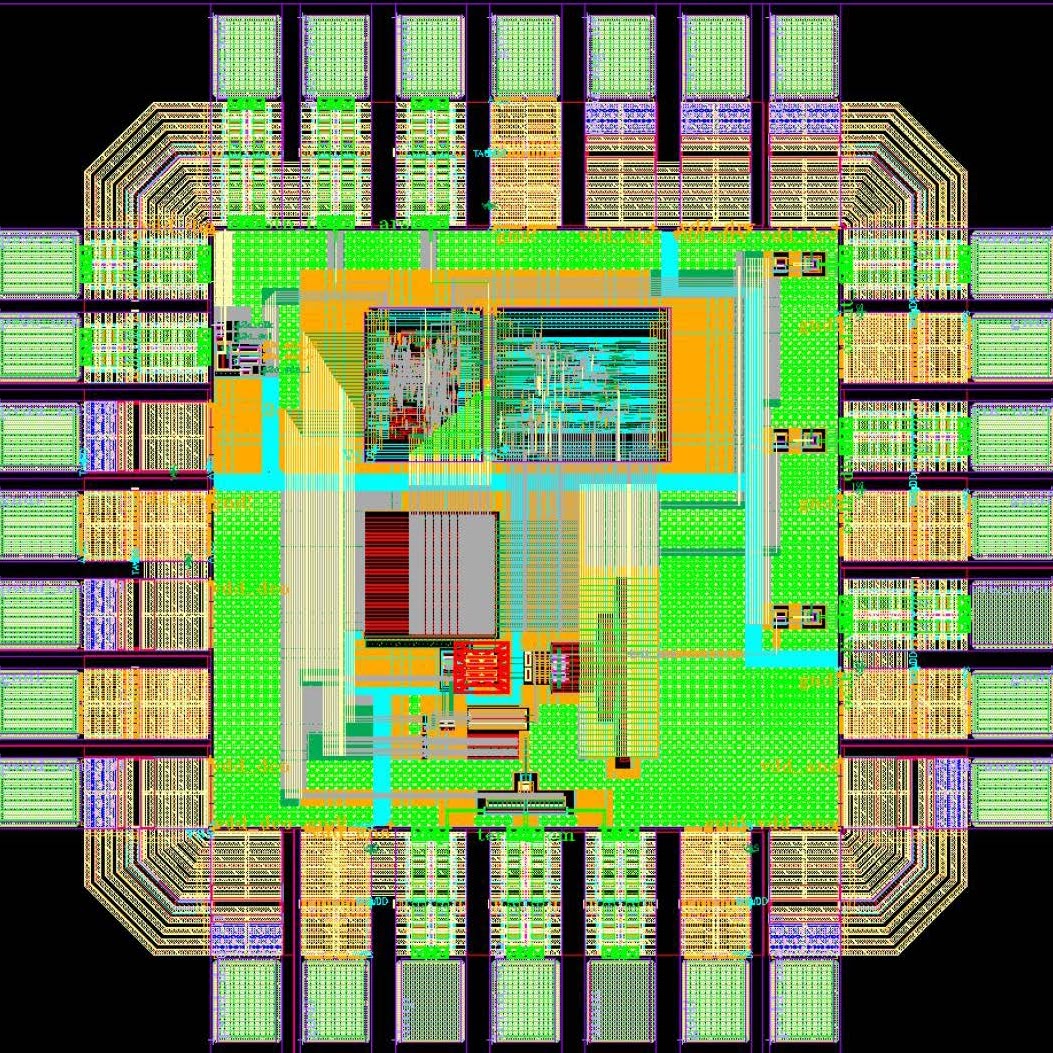

SRAM PIM Accelerator

- Date: Dec (65-nm T)'23

- Designer: Shin-Uk Kang

- Description: N/A

Adaptive Gain Controlled DPLL

- Date: Dec (65-nm T)'23

- Designer: In-Woo Jang

- Description: failed

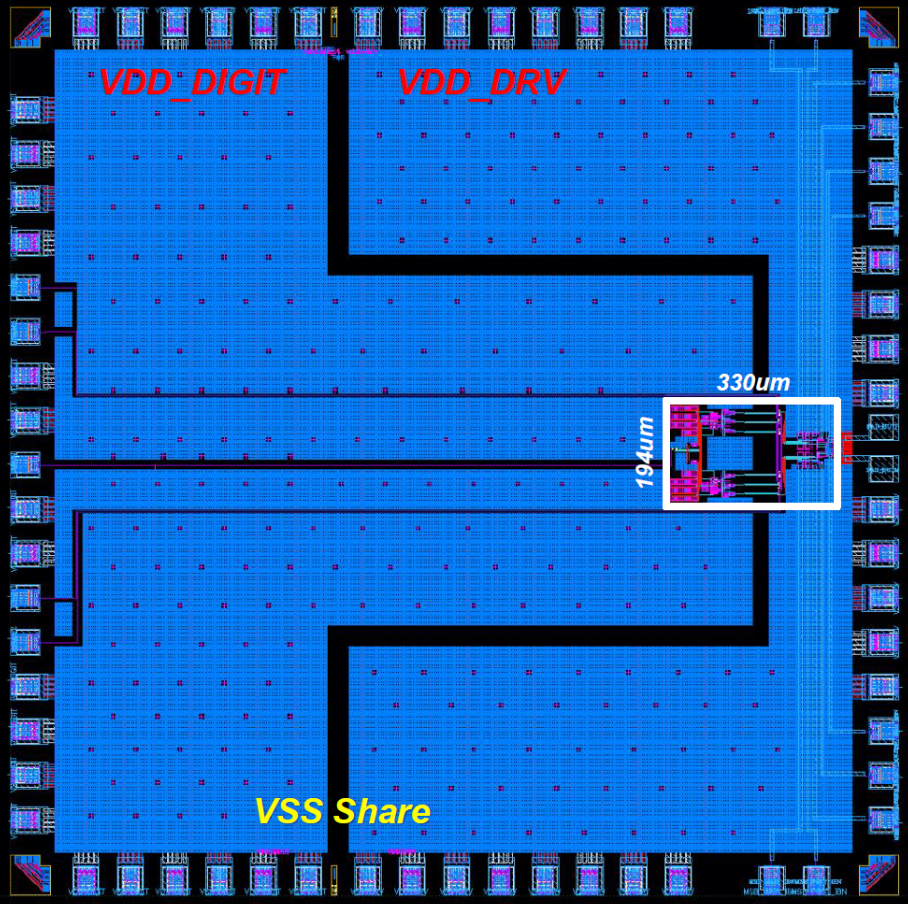

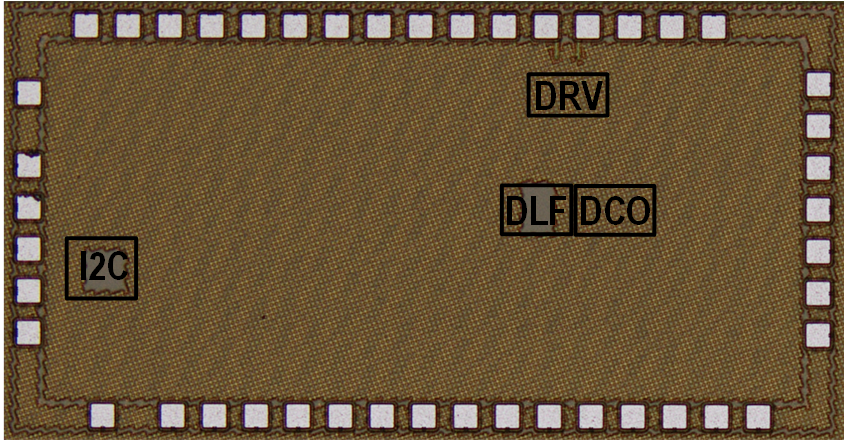

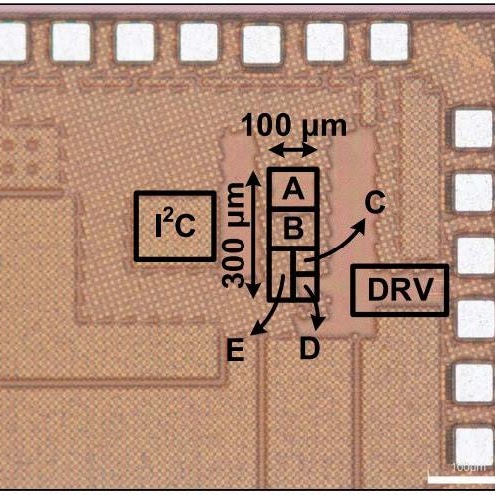

TX-PAM4-DRV

- Date: July (28-nm S)'23

- Designer: N/A

- Description: N/A

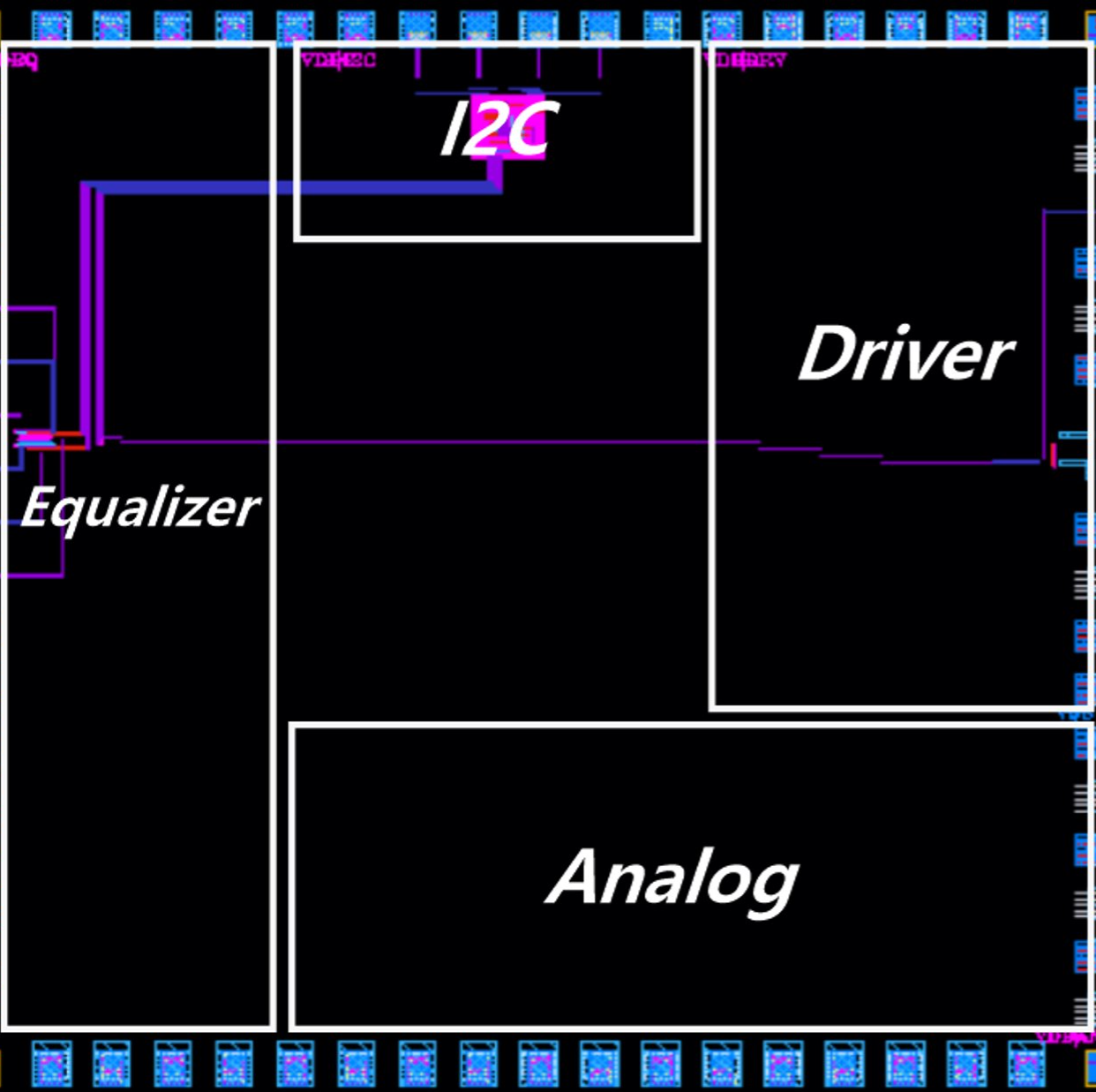

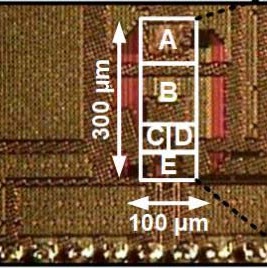

High-Speed Equalizer

- Date: July (28-nm S)'23

- Designer: N/A

- Description: N/A

ADPLL

- Date: Jan (28-nm S)'23

- Designer: Ji-Ho Kim

- Description: N/A

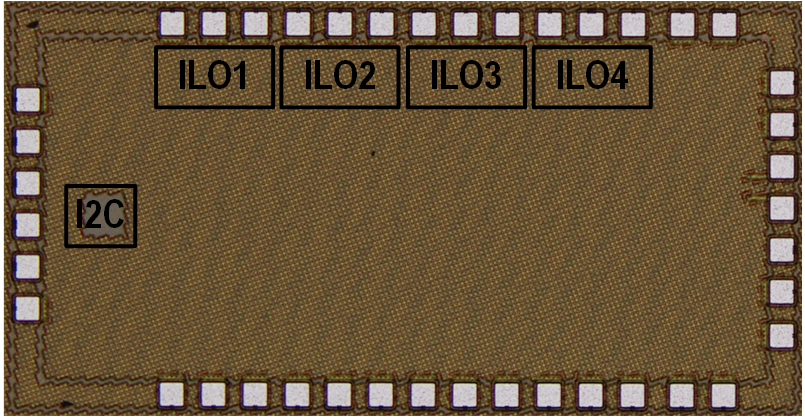

Injection Lock Oscillator (ILO)

- Date: Jan (28-nm S)'23

- Designer: Geun-Young Yu

- Description: N/A

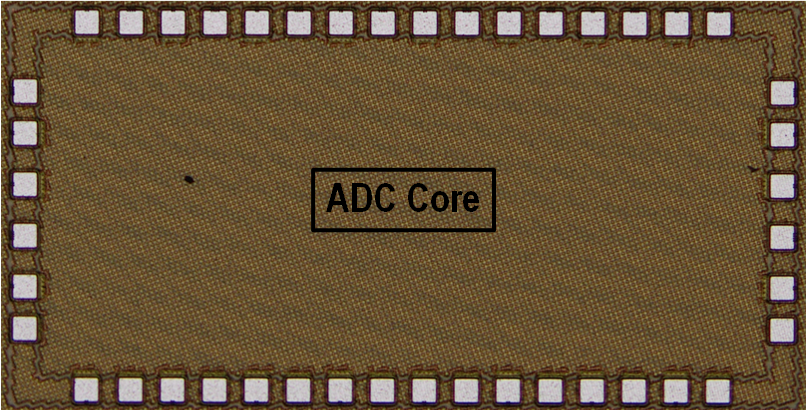

Flash ADC

- Date: Jan (28-nm S)'23

- Designer: Dong-Hoe Heo

- Description: N/A

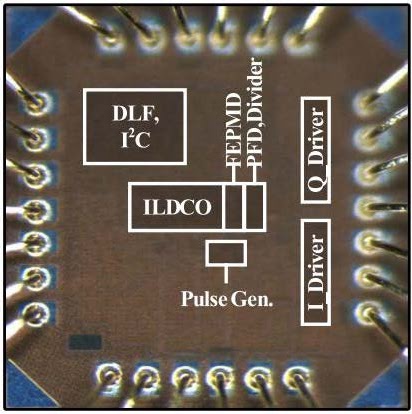

Clock Generator

- Date: ISSCC'17, JSSC'21

- Designer: N/A

- Description: N/A

.jpg)

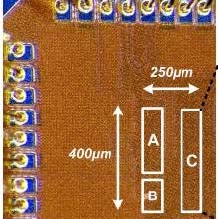

Clock and Data Recovery (CDR)

- Date: VLSI'19, JSSC'21

- Designer: N/A

- Description: N/A

Clock Generator

- Date: TCAS-II'19

- Designer: N/A

- Description: N/A

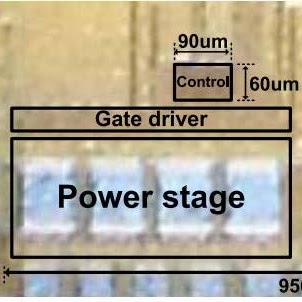

Power Regulator

- Date: ISSCC'19, SSC-L'19

- Designer: N/A

- Description: N/A

CDR

- Date: ASSCC'18, JSSC'19

- Designer: N/A

- Description: N/A

Clock Generator

- Date: TCAS-II'18

- Designer: N/A

- Description: N/A

Video Interface Receiver

- Date: TCAS-II'17

- Designer: N/A

- Description: N/A

Clock Generator

- Date: ESSCIRC'15, TCAS-I'18

- Designer: N/A

- Description: N/A

Clock Gen. & CDR

- Date: Failed'17

- Designer: N/A

- Description: N/A

CDR

- Date: Failed'16

- Designer: N/A

- Description: N/A

CDR

- Date: Failed'15

- Designer: N/A

- Description: N/A