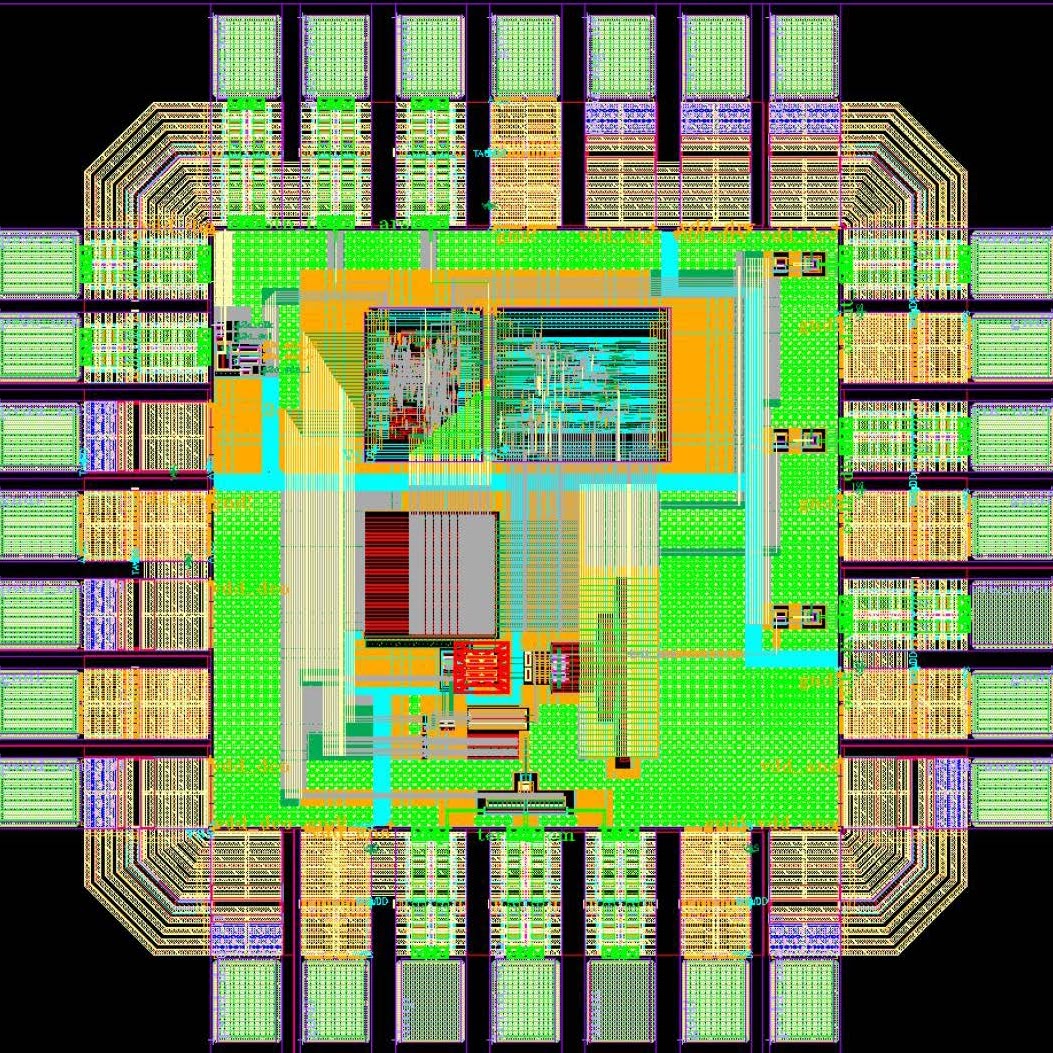

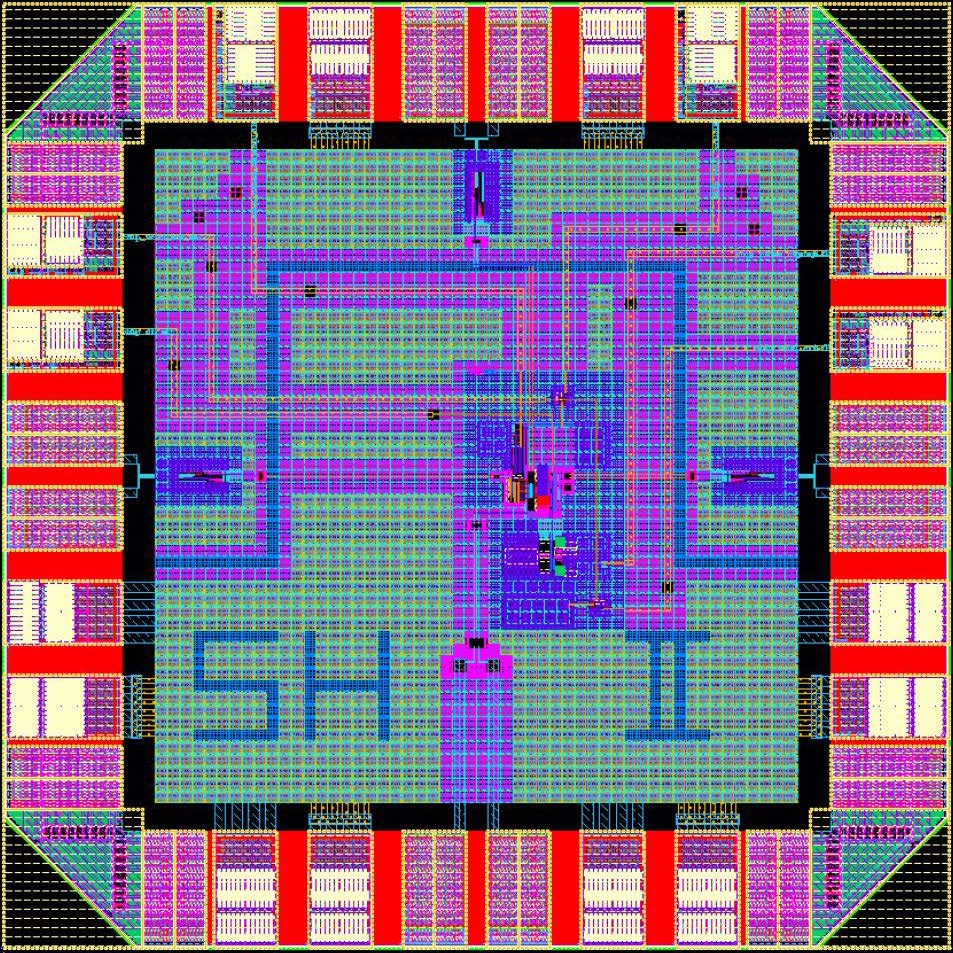

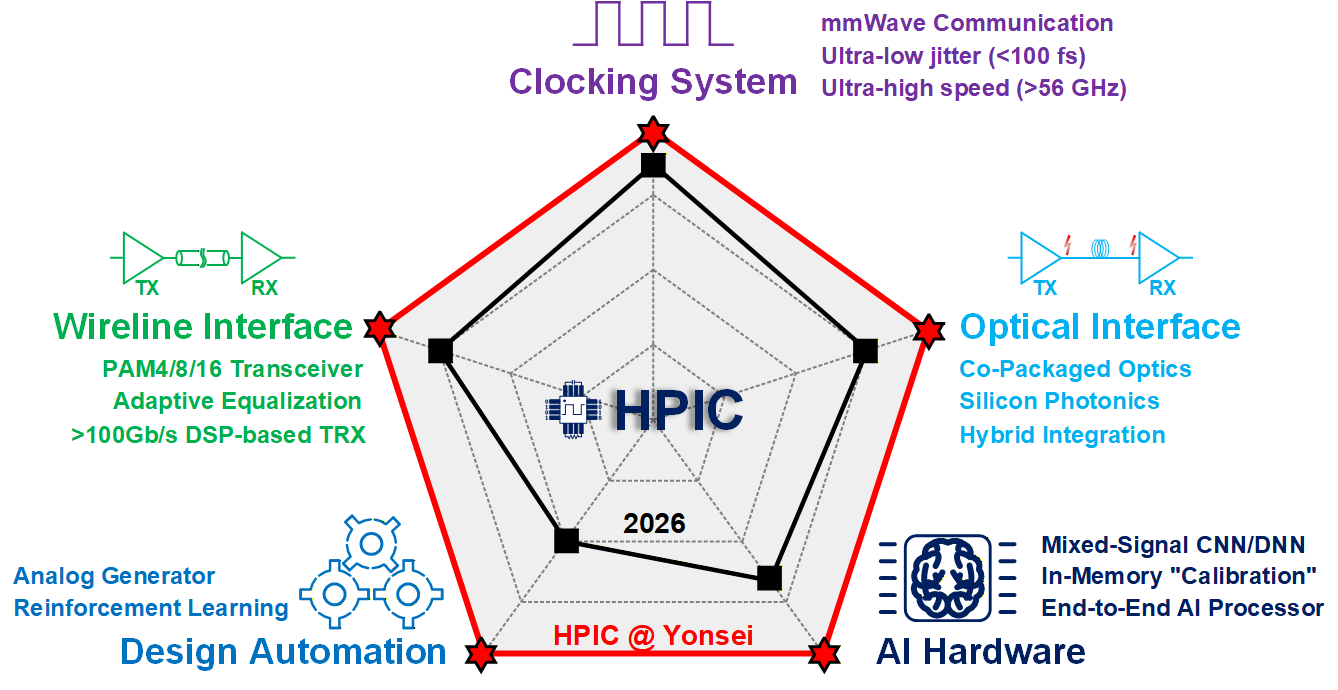

High-Performance Integrated Circuits

HPIC Design Lab

Welcome to HPIC at Yonsei University.

We focus on optimizing integrated circuits and systems for

high-performance computing.

Please see the

RESEARCH SECTION

for more information.

We are currently recruiting postdocs, graduate students, and

undergraduate interns.

If you are interested in HPIC Design Lab., don't hesitate to get

in touch with Min-Seong (mschoo@yonsei.ac.kr)

.jpg)